一种基于抗噪声模糊递归神经网络的FPGA实现方法

2025年6月20日

数园网络

404

申请号:CN202310350455.5

申请人:人工智能与数字经济广东省实验室(广州) | 华南理工大学

专利权人:人工智能与数字经济广东省实验室(广州) | 华南理工大学

申请日:2023-04-04

授权日:2023-08-08

专利类型:发明

法律状态:授权

发明人:张智军 | 何昊天 | 罗亚梅 | 张铭洋

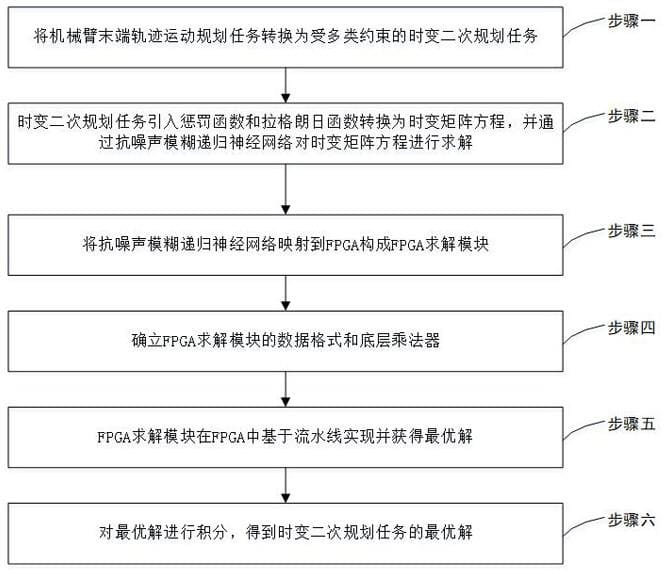

摘要:本发明公开一种基于抗噪声模糊递归神经网络的FPGA实现方法,包括以下步骤:将机械臂末端轨迹运动规划任务转换为受多类约束的时变二次规划任务;时变二次规划任务引入惩罚函数和拉格朗日函数转换为时变矩阵方程,并通过抗噪声模糊递归神经网络对时变矩阵方程进行求解;将抗噪声模糊递归神经网络映射到FPGA构成FPGA求解模块;确立FPGA求解模块的数据格式和底层乘法器;FPGA求解模块在FPGA中基于流水线实现并获得最优解;对最优解进行积分,得到时变二次规划任务的最优解。本发明的有益效果是:求解模块实时性好,计算速度快,效率更高,能够考虑多种约束条件。

摘要附图: